# Does Fully Homomorphic Encryption Need Compute Acceleration?

Leo de Castro<sup>1,\*</sup> Rashmi Agrawal<sup>2,3,\*,\$</sup> Rabia Yazicigil<sup>2</sup> Anantha Chandrakasan<sup>1</sup>

Vinod Vaikuntanathan<sup>1</sup> Chiraag Juvekar<sup>3</sup> Ajay Joshi<sup>2</sup>

<sup>1</sup>MIT, Cambridge, MA, USA; <sup>2</sup>Boston University, Boston MA, USA; <sup>3</sup>Analog Devices, Boston, MA USA {ldec, anantha, vinodv}@mit.edu, {rashmi23, rty, joshi}@bu.edu, chiraag.juvekar@analog.com

\*Equal Contribution \*Work done during internship at Analog Devices

Abstract—The emergence of cloud-computing has raised important privacy questions about the data that users share with remote servers. While data in transit is protected using standard techniques like Transport Layer Security (TLS), most cloud providers have unrestricted plaintext access to user data at the endpoint. Fully Homomorphic Encryption (FHE) offers one solution to this problem by allowing for arbitrarily complex computations on encrypted data without ever needing to decrypt it. Unfortunately, all known implementations of FHE require the addition of noise during encryption which grows during computation. As a result, sustaining deep computations requires a periodic noise reduction step known as bootstrapping. The cost of the bootstrapping operation is one of the primary barriers to the wide-spread adoption of FHE.

In this paper, we present an in-depth architectural analysis of the bootstrapping step in FHE. First, we observe that secure implementations of bootstrapping exhibit a low arithmetic intensity (< 1 Op/byte), require large caches (> 100MB) and as such, are heavily bound by the main memory bandwidth. Consequently, we demonstrate that existing workloads observe marginal performance gains from the design of bespoke highthroughput arithmetic units tailored to FHE. Secondly, we propose several cache-friendly algorithmic optimizations that improve the throughput in FHE bootstrapping by enabling up to  $3.2\times$  higher arithmetic intensity and  $4.6\times$  lower memory bandwidth. Our optimizations apply to a wide range of structurally similar computations such as private evaluation and training of machine learning models. Finally, we incorporate these optimizations into an architectural tool which, given a cache size, memory subsystem, the number of functional units and a desired security level, selects optimal cryptosystem parameters to maximize the bootstrapping throughput.

Our optimized bootstrapping implementation represents a best-case scenario for compute acceleration of FHE. We show that despite these optimizations, bootstrapping (as well as other applications with similar computational structure) continue to remain bottlenecked by main memory bandwidth. We thus conclude that secure FHE implementations need to look beyond accelerated compute for further performance improvements and to that end, we propose new research directions to address the underlying memory bottleneck. In summary, our answer to the titular question is: yes, but only after addressing the memory bottleneck!

# I. INTRODUCTION

The rapid development of cloud-based systems has enabled reliable and affordable access to shared computing resources at scale. However, this shared access raises substantial privacy and security challenges. Therefore, new techniques are required to guarantee the confidentiality of sensitive user data Outsourcing the Computation of  $f(x) = (x + \alpha)^2$

Fig. 1. Third-party cloud platform with outsourced FHE-based computing.

when it is sent to the cloud for processing. Fully Homomorphic Encryption (FHE) [15], [29] enables cloud operators to perform complex computations on encrypted user data without ever needing to decrypt it. The result of such FHE-based computation is in an encrypted form and can only be decrypted by the data owner. An illustrative use case of how a data owner can outsource computation on private data to an untrusted third-party cloud platform is shown in Figure 1.

While FHE-based privacy-preserving computing is promising, performing large encrypted computations with FHE still remains several orders of magnitude slower than operating on unencrypted data, which makes broad adoption impractical. This slowdown is an inherent feature of all existing lattice-based FHE schemes. All of these schemes produce ciphertexts containing a noise term, which is necessary for security. Each subsequent homomorphic operation performed on the ciphertext increases its noise, until it grows beyond a critical level after which recovery of the computation output is impossible. Sustained FHE computation thus requires a periodic de-noising procedure, called bootstrapping, to keep the noise below a correctness threshold. Unfortunately, this bootstrapping step is expensive in terms of both compute and memory requirements and is often  $> 100 \times$  more expensive than primitive operations like addition and multiplication on encrypted data.

Real-world applications commonly attempt to amortize this bootstrapping cost across multiple homomorphic operations. Even when considering these application-specific optimizations, bootstrapping consumes more than 50% of the total compute and memory budget for end-to-end operations like machine learning training [22]. To make FHE-based comput-

ing practical, we need to consider a multi-layer approach to accelerate both the bootstrapping step as well as its primitive building blocks using a combination of algorithmic and hardware techniques.

In this work, we first perform a thorough compute and memory analysis of both simple and complex FHE primitives including the bootstrapping step, with an intent to determine the limits and potential opportunities for accelerating FHE. Our analysis reveals that all FHE operations exhibit low arithmetic intensity (< 1 Op/byte) and require working-set sizes of hundreds of MB for practical and secure parameters. In fact, we observe that most existing performance optimization techniques for FHE often increase memory bandwidth requirements. These include both linear and non-linear operation optimizations proposed by Han and Ki [20], Han, Hhan and Cheon [18], and Bossuat, Mouchet, Troncoso-Pastoriza and Hubaux [3]. Recent bootstrapping implementation on GPUs by Jung, Kim, Ahn, Cheon and Lee [22] is the first work to perform memory-centric optimizations for linear operations in bootstrapping. Even after these optimizations, their implementation continues to be bounded by main memory bandwidth and exhibits an arithmetic intensity of < 1 Op/byte. On the other side of the design spectrum, recent work by Samardzic et al. [30] presents an architecture for a high-throughput hardware accelerator for FHE. This work primarily focuses on smaller parameter sets where full ciphertexts fit in on-chip cache memory allowing them to bypass the memory bandwidth limitation. However, many natural applications such as SIMD boostrapping, deep-neural network inference (with complex activation functions) and machine learning require larger parameter sets that are not addressed in [30].

In this work, we focus on presenting our three key contributions, i.e., application benchmarking, new techniques to improve memory performance, and evaluation of these techniques on end-to-end applications. More specifically:

- We present detailed benchmarking of the compute and memory requirements of various FHE computations ranging from primitive operations to end-to-end applications such as machine-learning training. We show that all these benchmarks exhibit low arithmetic intensity and require large working-sets in on-chip memory. We observe that these working-sets do not fit in the last level caches of today's reticle-limited chips leading to bootstrapping and other applications being bottlenecked by memory accesses.

- We next present techniques to improve main memory bandwidth utilization by effectively managing the moderate last-level cache provided by currently available commercial hardware. For cache-pressured hardware (<</li>

MB LLC) we propose a domain-specific physical address mapping to enhance DRAM utilization. We then present hardware-independent algorithmic optimizations that reduce memory and compute requirements of FHE operations.

- We finally propose an optimized, memory-aware cryptosystem parameter set that maximizes the throughput

TABLE I CKKS FHE PARAMETERS AND THEIR DESCRIPTION.

| Parameter                                   | Description                                                                                                                 |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| N                                           | Number of coefficients in a polynomial in the ciphertext ring.                                                              |

| n                                           | N/2, number of plaintext elements in a single cipher-                                                                       |

| 0                                           | text.                                                                                                                       |

| Q                                           | Full modulus of a ciphertext coefficient.                                                                                   |

| q                                           | Machine word sized prime modulus and a limb of $Q$ .                                                                        |

| $egin{array}{l} q \ \Delta \ P \end{array}$ | Scaling factor of a CKKS plaintext.                                                                                         |

| P                                           | Product of the additional limbs added for the raised modulus.                                                               |

| L                                           | Maximum number of limbs in a ciphertext.                                                                                    |

| $\ell$                                      | Current number of limbs in a ciphertext.                                                                                    |

| dnum                                        | Number of digits in the switching key.                                                                                      |

| $\alpha$                                    | $\lceil (L+1)/dnum \rceil$ . Number of limbs that comprise a                                                                |

|                                             | single digit in the key-switching decomposition. This                                                                       |

|                                             | value is fixed throughout the computation.                                                                                  |

| β                                           | $\lceil (\ell+1)/\alpha \rceil$ . An $\ell$ -limb polynomial is split into this number of digits during base decomposition. |

in FHE bootstrapping and logistic regression training by enabling up to  $3.2\times$  higher arithmetic intensity and  $4.6\times$  lower memory bandwidth.

The techniques that we propose often compose with prior art and can be used as drop-ins to provide performance improvements in existing implementations without the need for new hardware. Our proposed bootstrapping parameter set represents an upper limit on the performance of FHE operations that can be attained through pure compute acceleration when paired with existing state-of-art memory subsystems. Even with this optimal parameter set, we observe that the bootstrapping step is still primarily memory bound. Thus:

Our key conceptual take-away is that to accelerate FHE, we need novel techniques to address the underlying memory bandwidth issues. Compute acceleration alone is unlikely to make a dent.

Towards the goal of addressing memory bandwidth issues, we propose novel near-term algorithmic and architectural research directions.

# II. FULLY HOMOMORPHIC ENCRYPTION: THE API

To set the stage, in this section we present the operations implemented by the Cheon-Kim-Kim-Song (CKKS) [11] FHE scheme. We organize these operations in the form of an API that can be used by any application developer to design privacy-preserving applications. Specifying the CKKS scheme requires several parameters, and we summarize our notation for these parameters in Table I. Though we focus on the CKKS scheme, the API is generic and can be used for the BGV [5] and B/FV [4], [14] schemes as well<sup>1</sup>.

# A. Homomorphic Encryption API

The basic plaintext data-type in CKKS is a vector of length n where each entry is chosen from  $\mathbb{C}$ , the field of complex numbers. All arithmetic operations on plaintexts are

<sup>&</sup>lt;sup>1</sup>An exception is the Conjugate function, which the BGV and B/FV schemes do not support, since they do not encrypt complex numbers.

TABLE II

CKKS FULLY HOMOMORPHIC ENCRYPTION API.

| Operation Name                                                            | Output                                              | Implementation                                                      | Description                                                                   |

|---------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|

| $PtAdd(\llbracket \mathbf{x} \rrbracket, \mathbf{y})$                     | $[\![\mathbf{x}+\mathbf{y}]\!]$                     | $[\![\mathbf{x}]\!] + \mathbf{y}$                                   | Adds a plaintext vector to an encrypted vector.                               |

| $Add(\llbracket \mathbf{x} \rrbracket, \llbracket \mathbf{y} \rrbracket)$ | $[\mathbf{x} + \mathbf{y}]$                         | $\llbracket \mathbf{x}  rbracket + \llbracket \mathbf{y}  rbracket$ | Adds two encrypted vectors.                                                   |

| $PtMult(\llbracket \mathbf{x} \rrbracket, \mathbf{y})$                    | $\llbracket \mathbf{x} \cdot \mathbf{y} \rrbracket$ | Algorithm 1                                                         | Multiplies a plaintext vector and an encrypted vector.                        |

| $Mult(\llbracket \mathbf{x}  rbracket, \llbracket \mathbf{y}  rbracket)$  | $\llbracket \mathbf{x} \cdot \mathbf{y}  rbracket$  | Algorithm 2                                                         | Multiplies two encrypted vectors.                                             |

| $Rotate(\llbracket \mathbf{x}  rbracket, k)$                              | $\llbracket \phi_k(\mathbf{x}) \rrbracket$          | Algorithm 3                                                         | Rotates a vector by $k$ positions; see Section II-A for an illustration.      |

| $Conjugate([\![\mathbf{x}]\!])$                                           | $\llbracket \overline{\mathbf{x}}  rbracket$        | Algorithm 3 <sup>†</sup>                                            | Outputs an encryption of the complex conjugate of the encrypted input vector. |

<sup>†</sup> Through a clever encoding [11], the Conjugate operation implementation is identical to the Rotate implementation.

component-wise; the entries of the vector  $\mathbf{x} + \mathbf{y}$  (resp.  $\mathbf{x} \cdot \mathbf{y}$ ) are the component-wise sums (resp. products) of the entries of  $\mathbf{x}$  with the corresponding entries of  $\mathbf{y}$ . We denote the encryption of a length-n vector  $\mathbf{x}$  by  $[\![\mathbf{x}]\!]$ .

Table II gives a complete description of the API with the exception of the rotation operation, which we describe here. The Rotate operation takes in an encryption of a vector  $\mathbf{x}$  of length n and an integer  $0 \le k < n$ , and outputs an encryption of a rotation of the vector  $\mathbf{x}$  by k positions. As an example, when k=1, the rotation  $\phi_1(\mathbf{x})$  is defined as follows.

$$\mathbf{x} = (x_0 \ x_1 \ \dots \ x_{n-2} \ x_{n-1})$$

$$\phi_1(\mathbf{x}) = (x_{n-1} \ x_0 \ \dots \ x_{n-3} \ x_{n-2})$$

The Rotate operation is necessary for computations that operate on data residing in different slots of the encrypted vectors.

# B. Modular Arithmetic and the Residue Number System

Scalar Modular Arithmetic: Nearly all FHE operations reduce to scalar modular additions and scalar modular multiplications. Current CPU/GPU architectures do not implement modular arithmetic directly but emulate it via multiple arithmetic instructions, which significantly increases the amount of compute required for these operations. Therefore, optimizing modular arithmetic is critical to optimizing FHE computation.

To perform modular addition over operands that are already reduced, we use the standard approach of conditional subtraction if the addition overflows the modulus. For generic modular multiplications, we use the Barrett reduction technique [1]. When computing the sum of many scalars, we avoid performing a modular reduction until the end of the summation, as long as the unreduced sum fits in a machine word. As an optimization, we use Shoup's technique [31] for constant multiplication. That is, when computing  $x \cdot y \pmod{p}$  where x and p are known in advance, we can precompute a value  $x_s$  such that ModMulShoup $(x, y, x_s, p) = x \cdot y \pmod{p}$  is much faster than directly computing  $x \cdot y \pmod{p}$ .

Residue Number System (RNS): Often the scalars in homomorphic encryption schemes are very large, on the order of thousands of bits. To compute on such large numbers, we use the residue number system (also called the Chinese remainder representation) where we represent numbers modulo  $Q = \prod_{i=1}^{\ell} q_i$ , where each  $q_i$  is a prime number that fits in a standard machine word (less than 64 bits), as  $\ell$  numbers

modulo each of the  $q_i$ . We call the set  $\mathcal{B} := \{q_1, \dots, q_\ell\}$  an *RNS basis*. We refer to each  $q_i$  as a *limb* of Q.

This allows us to operate over values in  $\mathbb{Z}_Q$  without any native support for multi-precision arithmetic. Instead, we can represent  $x \in \mathbb{Z}_Q$  as a length- $\ell$  vector of scalars  $[x]_{\mathcal{B}} = (x_1, x_2, \ldots, x_\ell)$ , where  $x_i \equiv x \pmod{q_i}$ . We refer to each  $x_i$  as a limb of x. To add two values  $x, y \in \mathbb{Z}_Q$ , we have  $x_i + y_i \equiv x + y \pmod{q_i}$ . Similarly, we have  $x_i \cdot y_i \equiv x \cdot y \pmod{q_i}$ . This allows us to compute addition and multiplication over  $\mathbb{Z}_Q$  while only operating over standard machine words. The size of this representation of an element of  $\mathbb{Z}_Q$  is  $\ell$  machine words.

# C. CKKS Ciphertext Structure

In this section, we give the general structure of a ciphertext in the CKKS [11] homomorphic encryption scheme. A ciphertext is a pair of polynomials each of degree N-1. The coefficients of these ciphertexts are elements of  $\mathbb{Z}_Q$ , where Q has  $\ell$  limbs. Thus, in total, the size of a ciphertext is  $2N\ell$  machine words.

In CKKS, we are able to encrypt non-integer values, including complex numbers. The ciphertexts are "packed," which means they encrypt vectors in  $\mathbb{C}^n$ , where n=N/2, in a single ciphertext. For  $\mathbf{m}\in\mathbb{C}^n$ , we denote its encryption as  $[\![\mathbf{m}]\!]=(\mathbf{a_m},\mathbf{b_m})$  where  $\mathbf{a_m}$  and  $\mathbf{b_m}$  are the two polynomials that comprise the ciphertext. We omit the subscript  $\mathbf{m}$  when there is no cause for confusion.

An example of ciphertext parameters that achieve a 128-bit security level is  $N=2^{17}$  and  $\ell=35$ . With an 8-byte machine word, this gives a total ciphertext size of  $\sim 73.4$  MB. Note that in today's reticle-limited systems, the largest last-level cache size is 40 MB [28]. Consequently, we won't be able to fit even a single ciphertext in the last-level cache, which indicates the need for multiple expensive DRAM accesses when operating on ciphertexts.

Polynomial Representation: In order to enable fast polynomial multiplication, we will have all polynomials represented by default as a series of N evaluations at fixed roots of unity. This allows polynomial multiplication to occur in O(N) time. We refer to this representation as the evaluation representation. Certain subroutines, defined in section II-D, operate over the polynomial's coefficient representation, which is simply a vector of its coefficients. Addition of two polynomials and multiplication of a polynomial by a scalar are O(N) in both the coefficient and the evaluation representation. Moving

between representations requires a number-theoretic transform (NTT) or inverse NTT, which is the finite field version of the fast Fourier transform (FFT) and takes  $O(N \log N)$  time and O(N) space for a degree-(N-1) polynomial.

Encoding Plaintexts: CKKS supports non-integer messages, so all encoded messages must include a scaling factor  $\Delta$ . The scaling factor is usually the size of one of the limbs of the ciphertext, which is slightly less than a machine word. When multiplying messages together, this scaling factor grows as well. The scaling factor must be shrunk down in order to avoid overflowing the ciphertext coefficient modulus. We discuss how this procedure works in Section II-D.

#### D. Implementing the API

To implement the homomorphic API described in Table II, we need some "helper" subroutines. We first describe these subroutines and then provide the implementations of the homomorphic API using the subroutines.

Handling a Growing Scaling Factor: As mentioned in section II-C, all encoded messages in CKKS must have a scaling factor  $\Delta$ . In both the PtMult and Mult implementations, the multiplication of the encoded messages results in the product having a scaling factor of  $\Delta^2$ . Before these operations can complete, we must shrink the scaling factor back down to  $\Delta$  (or at least a value very close to  $\Delta$ ). If this operation is neglected, the scaling factor will eventually grow to overflow the ciphertext modulus, resulting in decryption failure.

To shrink the scaling factor, we divide the ciphertext by  $\Delta$  (or a value that is close to  $\Delta$ ) and round the result to the nearest integer. This operation, called ModDown, keeps the scaling factor of the ciphertext roughly the same throughout the computation.<sup>2</sup> For a more formal description, we refer the reader to [10]. We sometimes refer to a ModDown instruction that occurs at the end of an operation as Rescale.

Handling a Changing Decryption Key: In both the Mult and Rotate implementations, there is an intermediate ciphertext with a decryption key that differs from the decryption key of the input ciphertexts. In order to change this new decryption key back to the original decryption key, we perform a KeySwitch operation. This operation takes in a switching key  $ksk_{s\rightarrow s'}$  and a ciphertext  $[m]_s$  that is decryptable under a secret key s. The output of the KeySwitch operation is a ciphertext  $[m]_{s'}$  that encrypts the same message but is decryptable under a different key s'.

Key Switching [6]: Since the KeySwitch operation differs between Mult and Rotate, we do not define it separately. Instead, we go a level deeper, and define the subroutines necessary to implement KeySwitch for each of these operations. In addition to the ModDown operation, we use the ModUp operation, which allows us to add primes to our RNS basis. We follow the structure of the switching key in the work of

Han and Ki [20], where the switching key, parameterized by a length dnum, is a  $2 \times$  dnum matrix of polynomials.

$$ksk = \begin{pmatrix} \mathbf{a}_1 & \mathbf{a}_2 & \dots & \mathbf{a}_{dnum} \\ \mathbf{b}_1 & \mathbf{b}_2 & \dots & \mathbf{b}_{dnum} \end{pmatrix} \tag{1}$$

The KeySwitch operation requires that a polynomial be split into dnum "digits," then multiplied with the switching key. We define the function Decomp that splits a polynomial into dnum digits as well as a KSKInnerProd operation to multiply the dnum digits by the switching key.

Before proceeding further, we refer the reader to Table III where all the subroutines described above are defined in more detail. The implementation of the API functions are given in Algorithms 1, 2 and 3. We also give a batched rotation algorithm HRotate in Algorithm 4, which computes many rotations on the same ciphertext faster than applying Rotate independently several times.

```

\textbf{Algorithm 1} \; \mathsf{PtMult}(\llbracket \mathbf{m} \rrbracket, \mathbf{m}') = \llbracket \mathbf{m} \cdot \mathbf{m}' \rrbracket

```

- 1:  $(\mathbf{a}, \mathbf{b}) := \llbracket \mathbf{m} \rrbracket$

- 2:  $(\mathbf{u}, \mathbf{v}) := (\mathbf{a} \cdot (\Delta \cdot \mathbf{m}'), \mathbf{b} \cdot (\Delta \cdot \mathbf{m}'))$

- 3: **return**  $(ModDown_{\mathcal{B},1}(\mathbf{u}), ModDown_{\mathcal{B},1}(\mathbf{v})) \triangleright Rescale$

```

\textbf{Algorithm 2} \ \mathsf{Mult}(\llbracket \mathbf{m}_1 \rrbracket_{\mathbf{s}} \,, \llbracket \mathbf{m}_2 \rrbracket_{\mathbf{s}} \,, \mathsf{ksk_{\mathbf{s}^2 \to \mathbf{s}}}) = \llbracket \mathbf{m}_1 \cdot \mathbf{m}_2 \rrbracket_{\mathbf{s}}

```

- 1:  $(\mathbf{a}_1, \mathbf{b}_1) := \llbracket \mathbf{m}_1 \rrbracket_{\mathbf{s}}$

- 2:  $(\mathbf{a}_2, \mathbf{b}_2) := [\![ \mathbf{m}_2 ]\!]_{\mathbf{c}}$

- 3:  $(\mathbf{a}_3, \mathbf{b}_3, \mathbf{c}_3) := (\mathbf{a}_1 \mathbf{a}_2, \mathbf{a}_1 \mathbf{b}_2 + \mathbf{a}_2 \mathbf{b}_1, \mathbf{b}_1 \mathbf{b}_2)$

- 4:  $\overrightarrow{\mathbf{a}} := \mathsf{Decomp}_{\beta}(\mathbf{a}_3)$

- 5:  $\hat{\mathbf{a}}[i] := \mathsf{ModUp}(\overrightarrow{\mathbf{a}}[i]) \text{ for } 1 \leq i \leq \beta.$

- 6:  $(\hat{\mathbf{u}}, \hat{\mathbf{v}}) := \mathsf{KSKInnerProd}(\mathsf{ksk}_{\mathbf{s}^2 \to \mathbf{s}}, \hat{\mathbf{a}})$

- 7:  $(\mathbf{u}, \mathbf{v}) := (\mathsf{ModDown}(\hat{\mathbf{u}}), \mathsf{ModDown}(\hat{\mathbf{v}}))$

- 8:  $(\mathbf{a}', \mathbf{b}') := (\mathbf{b}_3 + \mathbf{u}, \mathbf{c}_3 + \mathbf{v})$

- 9: **return**  $(\mathsf{ModDown}_{\mathcal{B},1}(\mathbf{a}'), \mathsf{ModDown}_{\mathcal{B},1}(\mathbf{b}')) \triangleright \mathsf{Rescale}$

# **Algorithm 3** Rotate( $[\![\mathbf{m}]\!]_{\mathbf{s}}$ , k, $\mathsf{ksk}_{\psi_k(\mathbf{s})\to\mathbf{s}}$ ) = $[\![\phi_k(\mathbf{m})]\!]_{\mathbf{s}}$

- 1:  $(\mathbf{a}, \mathbf{b}) := [\![\mathbf{m}]\!]_{\mathbf{s}}$

- 2:  $(\mathbf{a}_{\mathsf{rot}}, \mathbf{b}_{\mathsf{rot}}) := (\mathsf{Automorph}(\mathbf{a}, k), \mathsf{Automorph}(\mathbf{b}, k))$

- 3:  $\overrightarrow{\mathbf{a}_{\mathsf{rot}}} := \mathsf{Decomp}_{\beta}(\mathbf{a}_{\mathsf{rot}})$   $\triangleright \beta \mathsf{ digits}.$

- 4:  $\hat{\mathbf{a}}[i] := \mathsf{ModUp}(\overrightarrow{\mathbf{a}_{\mathsf{rot}}}[i]) \text{ for } 1 \leq i \leq \beta.$

- 5:  $(\hat{\mathbf{u}}, \hat{\mathbf{v}}) := \mathsf{KSKInnerProd}(\mathsf{ksk}_{\psi_k(\mathbf{s}) \to \mathbf{s}}, \hat{\mathbf{a}})$

- 6:  $(\mathbf{u}, \mathbf{v}) := (\mathsf{ModDown}(\hat{\mathbf{u}}), \mathsf{ModDown}(\hat{\mathbf{v}}))$

- 7: **return**  $(\mathbf{u}, \mathbf{v} + \mathbf{b}_{\mathsf{rot}})$

Key Takeaway: The Shrinking Ciphertext Modulus A main observation coming out of our description of the homomorphic API is that the ciphertext modulus shrinks for each PtMult (algorithm 1) and Mult (algorithm 2) operation. This occurs in the ModDown operations at the end of these functions. If a ciphertext begins with L limbs, we can only compute a circuit with multiplicative depth L-1, since the ciphertext modulus shrinks by a number of limbs equal to the multiplicative depth of the circuit being homomorphically evaluated. This foreshadows the next section where we present an operation called bootstrapping [15] that increases the ciphertext modulus.

<sup>&</sup>lt;sup>2</sup>A better name for this operation would be "divide and mod-down" because it reduces the scaling factor *as well as* the ciphertext modulus. In this paper, we stick to the standard ModDown terminology for consistency with the literature.

TABLE III

CKKS Subroutines: These subroutines enable the implementation of the CKKS API defined in Table II.

| Sub-routine Name                                               | Output                                           | Used-in                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------|--------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ModDown_{\mathcal{B},d}([\mathbf{x}]_{\mathcal{B}})$          | $[\mathbf{x}/P+e]_{\mathcal{B}'}$                | PtMult<br>Mult<br>Rotate | This function takes in a polynomial ${\bf x}$ in the coefficient representation, where each coefficient is modulo $Q:=\prod_{q\in\mathcal{B}}q$ and represented in the RNS basis $\mathcal{B}=\{q_1,\dots,q_\ell\}$ . Assume that $d<\ell$ and let $P:=\prod_{i=\ell-d+1}^\ell q_i$ be the product of the last $d$ limbs of $\mathcal{B}$ . Let $\mathcal{B}'=\{q_1,\dots,q_{\ell-d}\}$ , and note that $Q/P=\prod_{q\in\mathcal{B}'}q$ . The output of this function is a polynomial $[{\bf y}]_{\mathcal{B}'}$ where each coefficient of ${\bf y}$ equals the corresponding coefficient of ${\bf x}$ divided by $P$ plus some small rounding error. |

| $ModUp_{\mathcal{B},\mathcal{B}'}([\mathbf{x}]_{\mathcal{B}})$ | $[\mathbf{x}]_{\mathcal{B}'}$                    | Mult<br>Rotate           | Takes a polynomial $\mathbf{x}$ where each coefficient is in the basis $\mathcal{B}$ and outputs the representation of $\mathbf{x}$ where each coefficient is in the basis $\mathcal{B}'$ . $\mathcal{B}$ could be a subset or superset of $\mathcal{B}'$ , or they could be unrelated. Note that this operation must also be performed in the coefficient representation.                                                                                                                                                                                                                                                                            |

| $Decomp_\beta(\mathbf{x})$                                     | $\{\mathbf{x}^{(1)},\ldots,\mathbf{x}^{(eta)}\}$ | Mult<br>Rotate           | Takes in a polynomial $\mathbf x$ and a parameter dnum and splits $\mathbf x$ into dnum digits. If $\mathbf x$ has $L$ limbs, each digit of $\mathbf x$ has roughly $\alpha:=\lceil (L+1)/dnum \rceil$ limbs.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $KSKInnerProd(ksk,\overrightarrow{\mathbf{x}})$                | $(\mathbf{a},\mathbf{b})$                        | Mult<br>Rotate           | Takes in a key-switching key ksk with the structure of eq. (1) and a vector of polynomials $\overrightarrow{x}$ of length dnum. Let ksk <sub>1</sub> be the first row of ksk and let ksk <sub>2</sub> be the second row of ksk. The output of this operation is two polynomials $\mathbf{a} := \langle ksk_1, \overrightarrow{x} \rangle$ and $\mathbf{b} := \langle ksk_2, \overrightarrow{x} \rangle$ .                                                                                                                                                                                                                                             |

| $Automorph(\mathbf{x},k)$                                      | $\psi_k(\mathbf{x})$                             | Rotate                   | Takes a vector $\mathbf x$ with $N$ elements and an integer $k$ and outputs a permutation $\psi_k(\cdot)$ of the elements. This permutation is an automorphism which is <i>not</i> simply a rotation; intuitively, the permutation $\psi_k$ of an encoded message will result in the decoded value being permuted by the natural rotation $\phi_k$ .                                                                                                                                                                                                                                                                                                  |

# Algorithm 4

$$\mathsf{HRotate}(\llbracket\mathbf{m}\rrbracket_{\mathbf{s}}, \{k_i, \mathsf{ksk}_{\psi_{k_i}(\mathbf{s}) \to \mathbf{s}}\}_{i=1}^r) = \{\llbracket\phi_{k_i}(\mathbf{m})\rrbracket_{\mathbf{s}}\}_{i=1}^r$$

```

1: (\mathbf{a}, \mathbf{b}) := [\![ \mathbf{m} ]\!]_{\mathbf{s}}

2: \overrightarrow{\mathbf{a}} := \mathsf{Decomp}_{\beta}(\mathbf{a})

\triangleright \beta digits.

3: \hat{\mathbf{a}}[j] := \mathsf{ModUp}(\overrightarrow{\mathbf{a}}[j]) \text{ for } 1 \leq j \leq \beta.

4: for i from 1 to r do

\hat{\mathbf{a}}_{\mathsf{rot}} := \mathsf{Automorph}(\hat{\mathbf{a}}, k_i) \text{ for } 1 \leq j \leq \beta

5:

(\hat{\mathbf{u}}, \hat{\mathbf{v}}) := \mathsf{KSKInnerProd}(\mathsf{ksk}_{\psi_{k:}(\mathbf{s})

ightarrow \mathbf{s}}, \hat{\mathbf{a}}_{\mathsf{rot}})

6:

(\mathbf{u}, \mathbf{v}) := (\mathsf{ModDown}(\hat{\mathbf{u}}), \mathsf{ModDown}(\hat{\mathbf{v}}))

7:

\mathbf{b}_{\mathsf{rot}} := \mathsf{Automorph}(\mathbf{b}, k_i)

8:

\llbracket \phi_{k_i}(\mathbf{m}) \rrbracket_{\mathbf{s}} := (\mathbf{u}, \mathbf{v} + \mathbf{b}_{\mathsf{rot}})

10: end for

11: return \{ \llbracket \phi_{k_i}(\mathbf{m}) \rrbracket_{\mathbf{s}} \}_{i=1}^r

```

# E. Concrete Costs

We present the hardware cost associated with various functions and subroutines in the FHE API in Table IV and Table V, and discuss the content of the tables briefly. To generate these performance numbers, we implement an architectural modeling tool that can perform an in-depth analysis given the number of functional units, cache size, and the memory subsystem parameters. In addition, our tool allows us to tune nearly all parameters of the algorithm, including N, dnum, and the maximum ciphertext modulus for a given security level.

Key Takeaway: Low Arithmetic Intensity. The key takeaway from the tables, in particular Table V, is that the arithmetic intensity, defined as the number of operations per byte transferred from DRAM, of all of the functions in the CKKS API is less than < 1 Op/byte. This means that when the ciphertexts do not fit in memory, any natural

application (e.g. logistic regression training, neural network evaluation, bootstrapping, etc.) built using these functions will have performance bounded by the memory bandwidth and not the computation speed.

Since our ciphertexts will remain too large to fit in the chip cache, much of this work will focus on improving the arithmetic intensity of CKKS bootstrapping. This translates to progressing further in the bootstrapping algorithm per memory transfer, which, in turn, translates to a faster bootstrapping implementation.

#### III. FULLY HOMOMORPHIC ENCRYPTION: APPLICATIONS

In this section, we describe how the FHE API from Section II can be leveraged to develop applications. As discussed in Section II-D, a CKKS ciphertext can only support computation up to a fixed multiplicative depth due to the shrinking ciphertext modulus. Once this depth is reached, a *bootstrapping* operation must be performed to grow the ciphertext modulus, which allows for computation to continue.

Many applications of interest have a deep circuit that requires bootstrapping multiple times: in general, machine learning training algorithms are good examples where deeper circuits for the training computation often lead to greater accuracy of the resulting model. In this section, we use *logistic regression training* over encrypted data as a running example to explain the process of FHE-based machine learning training. Logistic regression training contains both linear (e.g. inner-products) and non-linear (e.g. sigmoid) operations. The CKKS scheme naturally supports linear operations, while for non-linear operations we need to use a polynomial approximation (as in [19], [23]). The greater the degree of the polynomial, the greater the accuracy of the approximation, which further drives an increase in the circuit depth, in turn requiring bootstrapping.

#### TABLE IV

HARDWARE COST OF AUXILIARY SUBROUTINES: These benchmarks were taken for  $\log(N) = 17$ ,  $\ell = 35$ , dnum = 3. The **Total Operations** column counts the number of modular additions and multiplications in the operations, (note that this count for the Automorph function is zero). **GOP** stands for Giga operations. The **Total DRAM Transfers** is the sum of **DRAM Limb Reads**, **DRAM Limb Writes**, and **DRAM Key Reads**, the last of which counts the reads specifically for the switching keys. The KSKInnerProd operation has no limb writes because the limbs are immediately used in the next operation, the ModDown. The write is counted in the ModDown when the limbs are written out in to be read back in slot-wise format, as discussed in Section IV-A. The **Arithmetic Intensity** column defines the number of operations per byte transferred from DRAM.

| Sub-routine<br>Name | Total Operations (in GOP) | Total Mults<br>(in GOP) | Total DRAM<br>Transfers (in GB) | DRAM Limb<br>Reads (in GB) | DRAM Limb<br>Writes (in GB) | DRAM Key<br>Reads (in GB) | Arithmetic<br>Intensity<br>(in Op/byte) |

|---------------------|---------------------------|-------------------------|---------------------------------|----------------------------|-----------------------------|---------------------------|-----------------------------------------|

| ModDown             | 0.3000                    | 0.1288                  | 0.1877                          | 0.1007                     | 0.0870                      | 0                         | 1.59                                    |

| ModUp               | 0.2847                    | 0.1211                  | 0.1510                          | 0.0629                     | 0.0881                      | 0                         | 1.88                                    |

| Decomp              | 0.0092                    | 0.0092                  | 0.0734                          | 0.0367                     | 0.0367                      | 0                         | 0.12                                    |

| KSKInnerProd        | 0.0629                    | 0.0378                  | 0.4530                          | 0.1510                     | 0                           | 0.3020                    | 0.13                                    |

| Automorph           | 0                         | 0                       | 0.1468                          | 0.0734                     | 0.0734                      | 0                         | 0                                       |

#### TABLE V

HARDWARE COST OF FHE APIS: These benchmarks were taken for  $\log(N) = 17$ ,  $\ell = 35$ , dnum = 3. The number of rotations computed in the HRotate benchmark is 8. See the caption of Table IV for a description of the columns.

| Operation<br>Name | Total Operations<br>(in GOP) | Total Mults<br>(in GOP) | Total DRAM<br>Transfers(in GB) | DRAM Limb<br>Reads (in GB) | DRAM Limb<br>Writes (in GB) | DRAM Key<br>Reads (in GB) | Arithmetic Intensity<br>(in Op/byte) |

|-------------------|------------------------------|-------------------------|--------------------------------|----------------------------|-----------------------------|---------------------------|--------------------------------------|

| PtAdd             | 0.00459                      | 0                       | 0.1101                         | 0.0734                     | 0.0367                      | 0                         | 0.04                                 |

| Add               | 0.0092                       | 0                       | 0.2202                         | 0.1468                     | 0.0734                      | 0                         | 0.04                                 |

| PtMult            | 0.2747                       | 0.1098                  | 0.3282                         | 0.1835                     | 0.1447                      | 0                         | 0.84                                 |

| Mult              | 1.8333                       | 0.7826                  | 1.9293                         | 0.9070                     | 0.7203                      | 0.3020                    | 0.95                                 |

| Rotate            | 1.5310                       | 0.6682                  | 1.5645                         | 0.6501                     | 0.6124                      | 0.3020                    | 0.98                                 |

| Conjugate         | 1.5310                       | 0.6682                  | 1.5645                         | 0.6501                     | 0.6124                      | 0.3020                    | 0.98                                 |

| HRotate           | 6.2039                       | 2.7363                  | 8.1411                         | 3.2632                     | 2.4621                      | 2.4159                    | 0.76                                 |

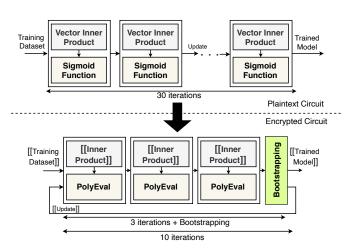

For our running example, we use the logistic regression training application given in Han, Song, Cheon and Park [19] and depicted in fig. 2. The training process is an iterative process that repeatedly computes an inner product followed by a sigmoid function on a training data set and the model weights. The logistic regression update equation is as follows.

$$\mathbf{w} \leftarrow \mathbf{w} + \frac{\mathsf{lr}}{n} \sum_{i=1}^{n} \sigma \left( \mathbf{z}_{i}^{T} \cdot \mathbf{w} \right) \cdot \mathbf{z}_{i}$$

(2)

The vector  $\mathbf{w}$  is the weight vector, the values n and  $\mathbf{r}$  are scalars, and  $\mathbf{z}_i$  represents the  $i^{th}$  vector of the training data set. The  $\sigma$  function is the sigmoid function.

To implement this iterative update, we split the update into two phases: a linear phase that contains the inner product<sup>3</sup> and a non-linear phase that contains the sigmoid function. We implement these phases separately with common building blocks shown in Table VI. The linear phase can be implemented with an InnerProduct routine that computes the inner product of two encrypted vectors. The non-linear phase is approximated with a polynomial, and the homomorphic evaluation of this polynomial can be implemented with PolyEval. The scalar products and summation can be implemented with the PtMult,

Mult, and Add functions. After some number of iterations, the encrypted weights are passed through the Bootstrap routine. The exact placement of the Bootstrap operation in a circuit is application-dependent. In our running example, bootstrapping needs to be done every three iterations (see Figure 2).

Fig. 2. Logistic regression training on encrypted data.

<sup>&</sup>lt;sup>3</sup>In the real implementation of Equation (2), these inner products are batched into a matrix-vector product. We use the same algorithm as [19].

TABLE VI

HOMOMORPHIC ENCRYPTION APPLICATION BUILDING BLOCKS: These building blocks are implemented using the API from Table 11.

| Name                                                                                        | Output                                         | Description                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\boxed{InnerProduct(\llbracket \mathbf{x} \rrbracket , \llbracket \mathbf{y} \rrbracket)}$ | $[\![\langle \mathbf{x},\mathbf{y}\rangle]\!]$ | Computes the inner product of two encrypted vectors. This computation is the specific encrypted inner product algorithm from Han et al. [19].                                                                                                                                                                                    |

| $- {PolyEval(\llbracket \mathbf{x} \rrbracket, p(\cdot))}$                                  | $[p(\mathbf{x})]$                              | This operation takes an encrypted vector $\mathbf{x}$ and a (univariate) polynomial $p$ as input. The result is an encryption of the evaluation of $p$ at $\mathbf{x}$ , where each entry of $p(\mathbf{x})$ is the evaluation of $p$ on the corresponding entry of $\mathbf{x}$ .                                               |

| $PtMatVecMult(\mathbf{M}, [\![\mathbf{x}]\!])$                                              | [Mx]                                           | This operation takes a plaintext matrix $M$ and multiplies it by an encrypted vector $\mathbf{x}$ . The result is an encryption of the vector $M\mathbf{x}$ . This is a major subroutine in Bootstrap.                                                                                                                           |

| $\overline{Bootstrap([\![\mathbf{x}]\!])}$                                                  | [[x]]                                          | This operation takes in an encryption of a vector $\mathbf{x}$ and outputs an encryption of the same vector $\mathbf{x}$ . This operation is necessary to be able to compute indefinitely on encrypted data. Far from being a null operation, this is nearly always the bottleneck operation when computing over encrypted data. |

### A. Bootstrapping

As discussed in Section II-D, the ciphertext modulus of CKKS shrinks with each multiplication. In order to compute indefinitely on a CKKS ciphertext, we must grow the ciphertext modulus without also growing the noise. This is not as simple as performing a ModUp function. The CKKS bootstrapping procedure [9] begins with this ModUp operation, which gives the new plaintext as  $\Delta \cdot \mathbf{m} + \mathbf{k}q$  where q is the modulus for the input ciphertext and  $\mathbf{k}$  is some polynomial with small integer coefficients. The primary goal of the bootstrapping operation is to homomorphically evaluate the modular reduction operation modulo q on this plaintext, returning the plaintext back to  $\Delta \cdot \mathbf{m}$ .

The CKKS bootstrapping algorithm follows a general structure that has remained relatively static in the literature [3], [8], [9], [18], [20] over the past few years. This structure has three main components: a linear operation, an approximation of the modular reduction function followed by another linear operation. The linear operations in bootstrapping require homomorphically evaluating the DFT on the encrypted data so that we perform modulus reduction on the coefficient representation of plaintext, rather than the evaluation (or slot) representation. The first of these DFT operations is called CoeffToSlot and the second is called SlotToCoeff. In between these two DFT operations is an approximation of the modular reduction function that consists of a polynomial evaluation followed by an exponentiation. For further details on polynomial evaluation and the exponentiation, we refer the readers to [3], [20].

To homomorphically evaluate the DFT, we use the observation that the DFT matrix can be factored into submatrices of smaller dimension. This turns the homomorphic DFT into a series of PtMatVecMult operations. However, there is a trade-off between the number of PtMatVecMult operations that must be computed and the size of the matrices in each PtMatVecMult instance. Each PtMatVecMult has a multiplicative depth of 1. The total dimension of the DFT is  $n=N/2=2^{16}$  for our parameters. Options to evaluate this DFT include evaluating a single PtMatVecMult with an  $n \times n$  input, which would require a very large number of rotations, or evaluating 16 PtMatVecMult instances in sequence with only two rotations

per instance. The former corresponds to treating DFT as a matrix-vector multiplication without using the structure of the DFT matrix while the latter corresponds to running the  $O(N \log N)$  algorithm for DFT.

We can interpolate between these two extremes to find the optimal depth vs. computation trade-off. Each sub-matrix in the factorization of the DFT matrix has a radix corresponding to the number of non-zero diagonals. The smaller the radix, fewer the rotations that must be computed during the PtMatVecMult instance. The rule is that the product of the radices of the PtMatVecMult iterations (in the DFT algorithm) must equal n. For example, for our parameter of  $n=2^{16}$ , this gives the options of three PtMatVecMult iterations with radices of  $2^5$ ,  $2^5$ , and  $2^6$ , or five PtMatVecMult iterations with four iterations having a radix of  $2^3$  matrix and one iteration with a radix of  $2^4$ . We call the number of iterations as fftlter. The homomorphic inverse DFT is computed in an analogous way.

Our approximation of the modular reduction function follows the literature, where we represent the modular reduction function modulo q with a sine function with period q, then approximate this sine function with a polynomial. We represent this polynomial with  $\operatorname{sine}(\cdot)$ , and we use the Chebyshev polynomial construction used in Han and Ki [20]. The degree of this polynomial is 63. We give a high-level pseudocode for the bootstrapping algorithm in Algorithm 5.

```

Algorithm 5 Bootstrap([\![\mathbf{x}]\!]) = [\![\mathbf{x}]\!]

```

```

1: (\mathbf{a}, \mathbf{b}) := [\![\mathbf{x}]\!]

2: [\![\mathbf{t}]\!] := \mathsf{ModUp}(\mathbf{a}, \mathbf{b})

3: for i from 1 to fftlter do \triangleright CoeffToSlot phase.

4: [\![\mathbf{t}]\!] \leftarrow \mathsf{PtMatVecMult}(\mathbf{M}_i, [\![\mathbf{t}]\!])

5: end for

6: [\![\mathbf{t}]\!] \leftarrow \mathsf{PolyEval}([\![\mathbf{t}]\!], \mathsf{sine}(\cdot))

7: for i from 1 to fftlter do \triangleright SlotToCoeff phase.

8: [\![\mathbf{t}]\!] \leftarrow \mathsf{PtMatVecMult}(\mathbf{M}_i, [\![\mathbf{t}]\!])

9: end for

10: return [\![\mathbf{t}]\!]

```

#### B. Concrete Costs

We give the concrete costs of the logistic regression and Bootstrap subroutines in Table VII and Table VIII respectively. As the table shows, the arithmetic intensity of the subroutines is less than 1 Op/byte. As discussed in Section II-E, since our ciphertexts do not fit in cache, this means that the performance of all sub-routines is bounded by the main memory bandwidth. In Table VII, we give benchmarks for the logistic regression implementation based on our architecture modeling discussed in Section II-E. The parameters we use are from the work of Jung et al. [22], and these parameters were chosen to optimize their secure logistic regression application that leverages a GPU implementation of CKKS bootstrapping. We refer to the original work of Han et al. [19] for the full algorithm benchmarked in Table VII. We note that the logistic regression iteration is the "most expensive" of the three iterations that follow a Bootstrap, since the ciphertexts in this iteration are the largest. As the ciphertext shrinks due to the reduced ciphertext modulus, the computation becomes cheaper. However, the arithmetic intensity remains essentially the same, and the performance of each phase of the algorithm is bottle-necked by the memory bandwidth. Overall, roughly half of the total runtime is spent in bootstrapping.

Key Takeaway: Bootstrapping is often the bottle-neck operation in HE applications, especially applications that implement a deep circuit. For example, even when using a heavily-optimized GPU implementation of bootstrapping, nearly half of the time in HE logistic regression training is spent on bootstrapping [22] (table VII). This motivates the need to optimize the Bootstrap operation to efficiently support deep circuits. Furthermore, the building blocks of bootstrapping are the same as many other HE applications; there are essentially no subroutines that are unique to bootstrapping. Many of the optimizations we give in Section IV and Section V apply more generally to HE applications.

### IV. CKKS BOOTSTRAPPING: CACHING OPTIMIZATIONS

In this section and section V, we present our optimizations to the CKKS bootstrapping algorithm. These optimizations fall into two categories: those that rely on hardware assumptions and those that do not. Our first class of optimizations assume a lower bound on the amount of available cache size relative to the size of the ciphertext limbs while second class of optimizations are more general as they reduce the total operation count of CKKS bootstrapping as well as the total number of DRAM reads, regardless of the hardware architecture.

This section focuses on the first set of optimizations. These caching optimizations do not affect the operation count of Bootstrap; instead, they reduce DRAM reads and writes to reduce the overall memory bandwidth requirement. Our optimizations demonstrate how best to utilize caches of various sizes relative to the size of the ciphertext limbs. We quantify the improvements of these optimizations in Section IV-E, where we give benchmarks for progressively larger cache sizes. Our baseline benchmark is the parameter set from the

GPU bootstrapping implementation of Jung et al. [22]. The parameters are given in Table XI.

# A. Caching O(1) Limbs

This is the first in a series of optimizations that details how best to utilize a cache for various cache sizes relative to the ciphertext limbs. We begin by discussing how to utilize a cache that can store a constant number of limbs. Intuitively, this optimization computes as much as possible on a single limb before writing it back to the main memory. This often involves performing the operations of several higher-level functions on a single limb before beginning the same sequence of operations on the next limb. This technique was referred to by Jung et al. [22] as a "fusing" of operations, and we include all fusing operations listed in their work in our bootstrapping algorithm. In addition, we provide a novel data mapping technique to handle caching data with different *data access patterns*.

Data Access Patterns: Having a small-cache (about 1-3 MB) in any FHE compute system has a caveat that must be carefully addressed. Some operations in CKKS such as NTT and iNTT operate on data within the slots of the same limb, independent of the other limbs in the ciphertext. On the other hand, RNS basis change operations in ModUp and ModDown require interaction between a certain number of slots across various limbs. This requires having a few slots from multiple limbs in on-chip memory to reduce the number of accesses to main memory for a single operation. To account for this, we define two different types of data access patterns. For the functions where limbs can be operated upon independently, we define the data access pattern as limb-wise and for the functions where slots can be operated upon independently, we define the data access pattern as slot-wise. A summary of this is given in Table IX. We have also illustrated this by giving a high-level pseudo code of ModUp in Algorithm 6. From this algorithm, it is evident that the ModUp operation includes both limb-wise and slot-wise operations, requiring a memory mapping that is efficient for both access patterns. A naive memory mapping would result in low throughput for at least one of these access patterns. Therefore, we describe a novel memory mapping approach to handle these two access patterns.

```

Algorithm 6 ModUp<sub>\mathcal{B},\mathcal{B}\cup\mathcal{B}'</sub> ([\mathbf{x}]_{\mathcal{B}}) = [\mathbf{x}]_{\mathcal{B}\cup\mathcal{B}'}

```

```

1: for i from 1 to |\mathcal{B}| do

2: [\mathbf{x}]_i \leftarrow \mathsf{iNTT}([\mathbf{x}]_i) \triangleright limb-wise

3: end for

4: for j from 1 to |\mathcal{B}'| do \triangleright Basis conversion.

5: [\mathbf{x}]_j \leftarrow \mathsf{NewLimb}_j([\mathbf{x}]_1, \dots, [\mathbf{x}]_{|\mathcal{B}|}) \triangleright slot-wise

6: end for

7: for j from 1 to |\mathcal{B}'| do

8: [\mathbf{x}]_j \leftarrow \mathsf{NTT}([\mathbf{x}]_j) \triangleright limb-wise

9: end for

10: return [\mathbf{x}]_{\mathcal{B} \cup \mathcal{B}'}

```

#### TABLE VII

HARDWARE COST OF FHE APPLICATIONS: These benchmarks were taken for  $\log(N)=17$ ,  $\ell=35$ , dnum =3. See the caption of Table IV for a description of the columns. The number of features in the logistic regression is d=256. The InnerProduct and PolyEval benchmarks are for the first iterations after a Bootstrap. The "Full LR Iteration" row is the first iteration of the training algorithm after a Bootstrap. The degree of the polynomial evaluated in PolyEval is 3.

| Sub-routine<br>Name | Total Operations (in GOP) | Total Mults<br>(in GOP) | Total DRAM<br>Transfers(in GB) | DRAM Limb<br>Reads (in GB) | DRAM Limb<br>Writes (in GB) | DRAM Key<br>Reads (in GB) | Arithmetic<br>Intensity<br>(in Op/byte) |

|---------------------|---------------------------|-------------------------|--------------------------------|----------------------------|-----------------------------|---------------------------|-----------------------------------------|

| InnerProduct        | 7.8558                    | 3.3806                  | 16.5413                        | 7.2918                     | 4.8455                      | 4.4040                    | 0.47                                    |

| PolyEval            | 2.9314                    | 1.2188                  | 3.5484                         | 1.7144                     | 1.3118                      | 0.5222                    | 0.83                                    |

| Full LR Iteration   | 92.4225                   | 39.6322                 | 195.052                        | 86.7822                    | 56.1387                     | 52.131                    | 0.47                                    |

| Bootstrap           | 149.546                   | 64.6859                 | 207.982                        | 109.91                     | 65.2434                     | 32.8288                   | 0.72                                    |

#### TABLE VIII

HARDWARE COST OF BOOTSTRAPPING: These benchmarks were taken for  $\log(N) = 17$ ,  $\ell = 35$ , dnum = 3. See the caption of Table IV for a description of the columns. These benchmarks represent the performance of the main sub-routines of bootstrapping. The degree of the polynomial in PolyEval is 63.

| Sub-routine<br>Name | Total Operations (in GOP) | Total Mults<br>(in GOP) | Total DRAM<br>Transfers(in GB) | DRAM Limb<br>Reads (in GB) | DRAM Limb<br>Writes (in GB) | DRAM Key<br>Reads (in GB) | Arithmetic<br>Intensity<br>(in Op/byte) |

|---------------------|---------------------------|-------------------------|--------------------------------|----------------------------|-----------------------------|---------------------------|-----------------------------------------|

| CoeffToSlot         | 58.486                    | 25.8087                 | 86.7424                        | 46.8651                    | 25.2875                     | 14.5899                   | 0.67                                    |

| PolyEval            | 57.834                    | 24.4496                 | 65.643                         | 33.0406                    | 23.744                      | 8.8584                    | 0.88                                    |

| SlotToCoeff         | 33.2265                   | 14.4275                 | 55.5001                        | 30.004                     | 16.1156                     | 9.3806                    | 0.59                                    |

TABLE IX

DATA DEPENDENCIES AND ACCESS PATTERN IN DIFFERENT FUNCTIONS

The NewLimb function is used in both ModUp and ModDown.

| Operation | Interaction | Independent | Access pattern |

|-----------|-------------|-------------|----------------|

| NTT, iNTT | Intra-limb  | Inter-limb  | limb-wise      |

| NewLimb   | Inter-limb  | Intra-limb  | slot-wise      |

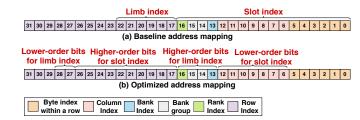

Physical Address Mapping: When we re-purpose the last level cache to support both limb-wise and slot-wise access patterns, we observe that the physical address mapping of the data in main memory has a substantial impact on the time it takes to transfer data from the main memory. Figure 3 (a) shows a natural physical address mapping for a ciphertext. We call this the baseline address mapping. Through simulations in DRAMSim3 [25] we notice that for this baseline address mapping, the limb-wise accesses require 2.3 ms to read 35 limbs worth of data. However, we notice that the slot-wise access pattern requires 9.2 ms to transfer the same amount of data. This is significantly lower as with the peak theoretical bandwidth (i.e., 19.2 GB/s) for DDR4 the time required to read 35 limbs worth of data is 1.9 ms.

There are two reasons for this performance hit while doing slot-wise accesses. With L=35, the size of the ciphertext is 36.7 MB whose limbs can be stored sequentially within a memory bank in one of the bank groups in main memory. Each limb of the ciphertext spans across multiple rows of the memory bank. Typically, each bank in main memory has a currently activated row whose contents are copied into a row buffer (acting as a cache) that can be accessed quickly. However, with slot-wise access pattern, every access is trying

Fig. 3. DDR4 physical address mapping. Baseline address mapping indexes all the slots  $(2^{17})$  using the lower-order 17 bits and all limbs using the immediate next 6 bits. In optimized physical address mapping, slots are indexed using 7 bits from the column and 10 bits from the row, accounting for  $2^{17}$  slots. The limbs are indexed using the 4 bits that index bank group, bank, and rank and 2 bits from the row index.

to read a different row, which takes longer because each row must be activated first. Moreover, with *slot-wise* accesses, we are unable to exploit the fact that bank accesses to different banks' groups require less time delay between accesses in comparison to the bank accesses within the same bank's group. Instead, we keep accessing data from the memory bank within the same bank group.

We propose an optimized physical address mapping as shown in Figure 3 (b). As shown in Table X, with this proposed address mapping, we observe that the *limb-wise* access requires a data transfer time of  $2.5\,$  ms, which is about 8% reduction in the times observed for the baseline *limb-wise* accesses. However, compared to the baseline *slot-wise* access pattern, our optimized *slot-wise* access pattern sees an increase in data transfer time by 76%, which is a significant improvement. We observe that the total data transfer time for baseline address mapping is about  $2.4\times$  higher than our optimized mapping. Our optimized physical

address mapping ensures that when performing *limb-wise* and *slot-wise* reads/writes, we exploit bank-level parallelism, and we focus on reducing the bank thrashing by not changing a bank's currently activated row frequently. Note that for a different DRAM type such as HBM2 or GDDR5/6, similar physical address mappings can be done to optimize the main memory bandwidth utilization.

TABLE X DRAM transfer times with Baseline and Optimized mapping for different access patterns: Transfer times are computed for reading L=35 limbs worth of data, which is 36.7 MB for our baseline parameter set.

| Mapping   | limb-wise<br>access | slot-wise<br>access | Total Time |

|-----------|---------------------|---------------------|------------|

| Baseline  | 2.3 ms              | 9.2 ms              | 11.5 ms    |

| Optimized | 2.5 ms              | 2.2 ms              | 4.7 ms     |

#### B. $\beta$ -Limb Caching

The next optimization considers a cache size that is  $O(\beta)$ . Recall that  $\beta$  is the number of digits generated from a polynomial key switching. We refer to Han and Ki [20] for more details. For our parameters where  $\beta \leq \text{dnum} = 3$ , this amounts to about 6 MB of cache. We need space for 3 limbs at all-times and 3 limbs worth of space to store intermediate results and other required constants. With this optimization, we can greatly reduce the number of accesses to main memory during key-switching.

Consider the HRotate function in Algorithm 4. There are  $\beta$  digits that are produced as the output of the ModUp operations. Naively, for each rotation we would read the limbs for each of the  $\beta$  digits, rotate them, then compute the inner product with the key-switching key. Since now we have space in the cache for  $\beta$  digits, we can instead pull in a single limb from each of the  $\beta$  outputs of ModUp, then compute the rotation and the inner product with the switching key limbs all at once. This allows us to read in the outputs of the ModUp function only once, regardless of the number of rotations computed.

### C. \alpha-Limb Caching

For this optimization, we assume that we have a relatively large LLC that can hold  $O(\alpha)$  limbs. Recall that  $\alpha$  is the number of limbs in a single digit after output by the Decomp function for key switching. We refer to Han and Ki [20] for more details. In practice, this optimization requires only slightly more than  $2\alpha$  limbs, using about 27 MB ( $2\alpha + 3$  MB) for  $\alpha = \lceil L + 1/\mathsf{dnum} \rceil = 12$  as L = 35 and  $\mathsf{dnum} = 3$ .

Under this assumption, we observe a dramatic decrease in the number of accesses to the main memory. This is because all of the *slot-wise* basis conversion operations in ModUp (line 5 in algorithm 6) and ModDown operate over  $\alpha$  limbs. If we can fit these  $\alpha$  limbs in cache, then we can generate new limbs in their entirety within the cache. With each new limb in cache, we can perform the NTT on the limb, which completes the basis change operation, and write this limb out to memory. This lets us generate all new limbs in evaluation

Fig. 4. DRAM transfers with various memory optimizations. As the cache size grows from left-to-right more optimizations become available. The impact is assessed cumulatively i.e. each successive optimization builds on top of the earlier ones. The order of the optimizations correspond to the order of the sections in Section IV.

format without having to write them out in *slot-wise* format and then reading them back in *limb-wise* format.

Accumulator Caching: We briefly mention an optimization that is easily enabled by a large cache but is also available with smaller caches  $(O(\beta))$  or even smaller). This optimization improves the memory bandwidth of the baby-step giant-step polynomial evaluation from Han and Ki [20]. A straightforward optimization is to cache the leaves (the baby-step) polynomials and reuse them to compute all of the giant-step limbs. However, if there is not enough space for the baby-step polynomials, we can still save DRAM reads by caching the partial sums of the giant step limb. When we read in a baby-step limb, we add this limb to all cached accumulators.

# D. Re-Ordering Limb Computations

For the ModDown operation, the limbs that are being reduced need additional operations to be performed on them. The ModDown operations in key switching and bootstrapping drop  $\alpha$  limbs. In this re-ordering optimization, we propose computing these  $\alpha$  limbs first so that the additional operations can be performed immediately. This optimization is especially potent when these  $\alpha$  limbs can be cached, since then there is no need to write out these limbs as they are being computed. Once we have the  $\alpha$  limbs, we can begin the ModDown operation by computing the output of the basis conversion. Then, for each subsequent limb that is computed, this limb can be immediately combined with the basis conversion output, saving DRAM transfers.

# E. Key Takeaway

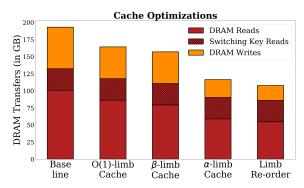

The benefits of the optimizations in this section are presented in Figure 4. As the figure shows, growing the cache size reduces the DRAM transfers of the bootstrapping algorithm by employing the optimizations described in this section. Note that the number of compute operations in the bootstrapping algorithm remains fixed for all these benchmarks.

# V. CKKS BOOTSTRAPPING: ALGORITHMIC OPTIMIZATIONS

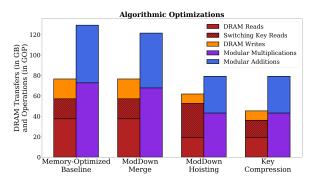

In this section, we present our algorithmic optimizations to the CKKS bootstrapping algorithm. These optimizations represent strict improvements to the CKKS bootstrapping algorithm and they do not depend on the cache size. However, as an added benefit of reducing the compute operation count, they also reduce the memory bandwidth, as displayed in Figure 5.

Our baseline for demonstrating the improvements of these optimizations is the memory-optimized algorithm from Section IV. Therefore, the left-most baseline bar in Figure 5 contains all of the memory optimizations described in Section IV. For the algorithm that includes all of our optimizations, we performed a parameter search to optimize the bootstrapping throughput for a 128-bit security level. We discuss our parameter search method further in Section VI. These parameters are given in Table XI, and all benchmarks in Figure 5 were taken using these same parameters.

# A. Combining ModDown and Rescale in Mult

This optimization merges the two ModDown operations in lines 7 and 9 in Algorithm 2. To merge these ModDown operations, we must lift the addition step in line 8 above the first ModDown. We achieve this by modifying the double-hoisting method from Bossuat et al. [3], multiplying the two polynomials by P to efficiently lift the two polynomial to the modulus PQ. We denote the operation that multiplies by P modulo Q and then interprets the result modulo PQ as PModUp. By applying the PModUp function, we can move the addition above the first ModDown, making the two ModDown operations adjacent, which allows them to be combined. This new Mult algorithm, denoted as NewMult, is given in Algorithm 7, and the lines in blue denote the differences from Algorithm 2.

Faster Encrypted Inner Product: As a direct result of this optimization, we obtain a faster encrypted inner product. Consider the operation that computes  $[\![\mathbf{z}]\!] = \sum_i \mathsf{Mult}([\![\mathbf{x}_i]\!], [\![\mathbf{y}_i]\!])$  where  $[\![\mathbf{x}]\!]$  and  $[\![\mathbf{y}]\!]$  are vectors of ciphertexts. Using the NewMult operation, we need to compute only one ModDown operation over the entire sum. This is because we can merge the additions in line 8 to sum all of the polynomials before any ModDown is computed.

```

\begin{split} & \underset{1: \ (\mathbf{a}_{1}, \mathbf{b}_{1}) := \ [\![\mathbf{m}_{1}]\!]_{\mathbf{s}}}{\mathbf{1}: \ (\mathbf{a}_{1}, \mathbf{b}_{1}) := \ [\![\mathbf{m}_{1}]\!]_{\mathbf{s}}} \\ & \underset{2: \ (\mathbf{a}_{2}, \mathbf{b}_{2}) := \ [\![\mathbf{m}_{2}]\!]_{\mathbf{s}}}{\mathbf{1}: \ (\mathbf{a}_{3}, \mathbf{b}_{3}, \mathbf{c}_{3}) := \ (\mathbf{a}_{1}\mathbf{a}_{2}, \mathbf{a}_{1}\mathbf{b}_{2} + \mathbf{a}_{2}\mathbf{b}_{1}, \mathbf{b}_{1}\mathbf{b}_{2})} \\ & \underset{3: \ (\mathbf{a}_{3}, \mathbf{b}_{3}, \mathbf{c}_{3}) := \ (\mathbf{a}_{1}\mathbf{a}_{2}, \mathbf{a}_{1}\mathbf{b}_{2} + \mathbf{a}_{2}\mathbf{b}_{1}, \mathbf{b}_{1}\mathbf{b}_{2})} \\ & \underset{5: \ \hat{\mathbf{a}}_{i} := \ \mathsf{Decomp}_{\mathsf{dnum}}(\mathbf{a}_{3})}{\mathsf{dec}} \\ & \underset{5: \ \hat{\mathbf{a}}_{i} := \ \mathsf{ModUp}(\vec{\mathbf{a}}[i]) \ \ \mathsf{for} \ 1 \le i \le \mathsf{dnum}.} \\ & \underset{6: \ (\hat{\mathbf{u}}, \hat{\mathbf{v}}) := \ \mathsf{KSKInnerProd}(\mathsf{ksk}_{\mathbf{s}^{2} \to \mathbf{s}}, \hat{\mathbf{a}})}{\mathsf{7}: \ (\hat{\mathbf{b}}_{3}, \hat{\mathbf{c}}_{3}) := \ (\mathsf{PModUp}(\mathbf{b}_{3}), \mathsf{PModUp}(\mathbf{c}_{3}))} \\ & \underset{8: \ \textbf{return} \ \ (\mathsf{ModDown}(\hat{\mathbf{u}} + \hat{\mathbf{b}}_{3}), \mathsf{ModDown}(\hat{\mathbf{v}} + \hat{\mathbf{c}}_{3}))}{\mathsf{NodDown}(\hat{\mathbf{v}} + \hat{\mathbf{c}}_{3}))} \end{aligned}

```

#### B. Hoisting the ModDown in PtMatVecMult

In section II-D, we discussed how r rotations on the same ciphertext can be computed more efficiently than simply applying the Rotate function r times. This function HRotate described in Algorithm 4 achieves an improved performance

by identifying an expensive common subroutine in all of the Rotate operations: the ModUp routine.

Bossuat et al. [3] present an optimization that hoists the second *slot-wise* operation in the function: the ModDown routine. However, their technique is similar to the one in NewMult, where the message polynomial is lifted to the raised modulus via the inexpensive PModUp procedure. They call this optimization "double-hoisting." Our ModDown hoisting optimization is used in the context of a baby-step giant-step (BSGS) algorithm that implements PtMatVecMult. The trade-off in this algorithm is that a larger baby-step and a smaller giant step means more DRAM reads for the switching keys, while a smaller baby-step and a larger giant step means more DRAM reads for the ciphertexts, since the baby-step ciphertexts must be read in for each giant-step.

In Section V-C, we give a simple optimization to compress the size of the keys by a factor of 2. Using our architecture modeling tool, we determine that this optimization shifts the balance between the baby-step size and the giant-step size so significantly that the optimal number of giant steps is 1. This essentially collapses the baby-step giant-step structure into just a single step that computes all r iterations at once. Therefore, by removing the giant steps in the BSGS algorithm, the PtMatVecMult collapses into a single instance of HRotate that includes the PModUp double-hoisting optimization, which allows the PtMult to be absorbed into the inner loop. This algorithm is given in Algorithm 8, and the lines that differ from HRotate are in blue.

```

Algorithm 8 PtMatVecMult(\mathbf{M}, [\![\mathbf{x}]\!], \{k_i, \mathsf{ksk}_i\}_{i=1}^r) = [\![\mathbf{Mx}]\!]

1: (\mathbf{a}_{\mathbf{x}}, \mathbf{b}_{\mathbf{x}}) := [\![\mathbf{x}]\!]_{\mathbf{s}}

2: \overrightarrow{\mathbf{a}_{\mathbf{x}}} := \mathsf{Decomp}_{\beta}(\mathbf{a}_{\mathbf{x}})

\triangleright \beta digits.

3: \hat{\mathbf{a}}_j := \mathsf{ModUp}(\overrightarrow{\mathbf{a}_{\mathbf{x}}}^{(i)}) \text{ for } 1 \leq j \leq \beta.

4: (\hat{\mathbf{a}}_{\mathbf{v}}, \hat{\mathbf{b}}_{\mathbf{v}}) \leftarrow 0, 0

\triangleright We will have \mathbf{y} = \mathbf{M}\mathbf{x}.

5: for i from 1 to r do

\hat{\mathbf{a}}_{\mathsf{rot}}^{(j)} := \mathsf{Automorph}(\hat{\mathbf{a}}_j, k_i) \text{ for } \underbrace{1 \leq j \leq \beta}

6:

(\hat{\mathbf{u}}, \hat{\mathbf{v}}) := \mathsf{KSKInnerProd}(\mathsf{ksk}_i, \hat{\mathbf{a}}_\mathsf{rot})

7:

8:

\mathbf{b}_{\mathsf{rot}} := \mathsf{Automorph}(\mathbf{b_m}, k_i)

\hat{\mathbf{b}}_{\mathsf{rot}}, \hat{\mathbf{M}}_i \leftarrow \mathsf{PModUp}(\mathbf{b}_{\mathsf{rot}}), \mathsf{PModUp}(\Delta \cdot \mathbf{M}_i)

9:

ightarrow \mathbf{M}_i is the i^{th} non-zero diagonal of \mathbf{M}

10:

(\hat{\mathbf{a}}_{\mathbf{v}}, \hat{\mathbf{b}}_{\mathbf{v}}) += \hat{\mathbf{M}}_i \cdot (\hat{\mathbf{u}}, \hat{\mathbf{v}} + \hat{\mathbf{b}}_{\mathsf{rot}})

⊳ PtMult

11:

12: end for

13: return (ModDown(\hat{\mathbf{a}}_{\mathbf{v}}), ModDown(\hat{\mathbf{b}}_{\mathbf{v}}))

```

Removing Giant-Steps Beyond Bootstrapping: This optimization is not a bootstrapping-only optimization. The hoisting optimizations that are described for PtMatVecMult for bootstrapping are more broadly applicable to the InnerProduct computation. When multiple InnerProduct operations needs to be performed in parallel, this hoisting optimization can be amortized across these parallel InnerProduct computations, which results in about 35% improvement in logistic regression training iterations for our running example.